###

## 低誘電率材料の価電子 EELS を 用いた誘電率測定

# Dielectric Constant Measurement of Low-k Interconnect Dielectrics by Valence Electron Energy Loss Spectroscopy (VEELS)

大塚 祐二<sup>a</sup>,川崎 直彦<sup>a</sup>,迫 秀樹<sup>a</sup>,小川 真一<sup>b</sup> Yuji Otsuka, Naohiko Kawasaki, Hideki Sako and Shinichi Ogawa

> <sup>a</sup>東レリサーチセンター形態科学研究部 <sup>b</sup>産業技術総合研究所

要 旨 超集積 (ULSI) 電子デバイス中の低誘電率 (low-k) 膜の配線加工プロセス中に生じた局所ダメージ構造について,価電子エネルギー損失分光法 (Valence Electron Energy Loss Spectroscopy, VEELS) を用いた誘電率測定を実施した.加速電圧 80 kV における測定により,チェレンコフ放射による低エネルギー損失領域のスペクトル変調を抑制し,薄膜厚さ制御によるエネルギー損失関数の正確な導出の結果,配線側壁付近約 10 nm 領域での,加工プロセスダメージに起因すると思われる誘電率上昇を検出することができた.

キーワード: 価電子エネルギー損失分光法、VEELS、低誘電率膜、 クラマースークローニッヒ解析、KKA

#### 1. はじめに

電子エネルギー損失分光法(EELS)は,燃料電池電極触媒や超集積電子デバイスなどのナノメートル領域での評価などに,極めて有効な手法である。EELS からは,単に組成の情報だけでなく,局所における化学状態や電子構造に関する情報も得る事が可能である $^{1)}$ . 多くの場合,EELS は内殻電子励起の信号を用いた高空間分解能での組成分析や,X線吸収分光法(XAS)と同様にエネルギー損失吸収端微細構造(Energy Loss Near Edge Structure; ELNES)を用いた電子状態解析が実施されている $^{2\sim4}$ )、特に,最近の球面収差補正機構を具備した TEM/STEM 装置の開発により,これらの評価が原子カラム分解能で実施できるまでになってきた $^{5\sim7}$ . 一方では,EELS 手法の発展とともに,有機材料などを含めた先端材料解析にとっては,清浄な試料作製技術や照射損傷を極小にすることもより一層重要な課題となっている.

°〒520-8567 滋賀県大津市3-3-7 TEL: 077-533-8629; FAX: 077-533-8628 E-mail: yuji\_otsuka@trc.toray.co.jp 2012年3月5日受付 TEM ベースの EELS においては、低エネルギー損失領域に存在する価電子励起の情報(Valence EELS: VEELS)も取得することが可能である。VEELS を用いると、試料厚さの情報<sup>8)</sup>、バンドギャップエネルギーの測定<sup>9)</sup>、そしてクラマースークローニッヒ解析(Kramers-Kronig Analysis: KKA)を用いた複素誘電関数や光学定数の測定<sup>10)</sup> が実施可能である。VEELS においては、低エネルギー損失領域の非局在化の問題<sup>11)</sup> により、内殻損失領域での EELS (Core EELS: CEELS) のように原子カラム分解能での測定は不可能であるが、通常の CEELS より二桁程度少ない電子線照射量での測定が可能であるため、はるかに短時間に低ダメージでの測定が行えるという利点がある。特に、結晶構造解析ができない非晶性材料の評価には、KKA による誘電率や屈折率の局所抽出には、広範なニーズが存在すると考える。

しかしながら、実際に VEELS を用いた未知物質の誘電関数の導出を行う場合には、2つの大きな問題がある。ひとつは $0\sim 5$  eV 付近の低エネルギー損失領域における、チェレンコフ放射  $^{12}$  などのいわゆる遅延効果(Retardation Effect)の影響であり、これらは誘電関数やバンドギャップエネルギーの測定結果を大きく変容させてしまう可能性がある。もうひとつは、KKA における規格化プロセス精度の低さである。未知物質からのエネルギー損失関数導出の際の規格化においては、試料膜厚を用いる方法が提案されている  $^{13}$  が、実際に正確な膜厚を測定することは容易ではない。

本稿では、通常のシリコン系デバイスで絶縁材料として用 いられている  $SiO_2$  よりも、低い誘電率を持つ low-k 材料を 微細配線間に用いた試料に対して、VEELS 測定により局所 誘電率測定を実施した結果について報告する. Low-k 材料は、 極小化する Cu 配線の高速動作には必要不可欠なものであり、 メチルシロセスキオキサン (MSQ) などの多孔性 Si-O-C (p-SiOC) やシリカベースの材料などが広く開発・検討され ている14. しかしながら、実際の配線プロセスである、ドラ イエッチングやアッシング,洗浄,金属堆積などの工程で, これら材料の電気的、物理的特性は容易に変質してしまうた め、たとえば配線の側壁近傍などの局所領域で、これら材料 の配線プロセスによる変質を評価することは非常に重要にな るのである. これまで、TEM 観察と組み合わせた CEELS による、加工損傷領域のlow-k膜の評価が行なわれてき た<sup>15,16)</sup> が、p-SiOC タイプの加工損傷の評価は、カーボン脱 離のような組成比の変化を捉えるのみであり、結合状態など の構造変化に関する情報を得ることは出来なかった、最近 我々は、クライオ条件での EELS 測定を用いて、加工損傷領 域で C = C 二重結合の生成を報告した<sup>17)</sup> が,これらの冷却 測定は、日常的な評価に用いることが容易ではない手段であ る. ULSI 素子の配線素子開発においては、パターニングさ れた low-k 膜の誘電率の局所変動に関する直接的な情報こそ が求められているのである.

本稿では、VEELS を用いた low-k 層間絶縁膜の局所誘電率 (k) の導出手順について、上述した二つの問題への検討

結果を含めて紹介する. すなわち, ①最適(低ダメージ)な 試料作製, ②チェレンコフ放射の影響の検証と極小化, ③正 確な膜厚測定・制御による KKA 規格化プロセスの高精度化, を適用することで, 1 nm 程度の高空間分解能で局所誘電率 測定が実施できることを示す.

#### 2. 実験方法

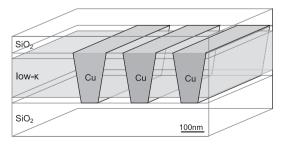

試料には、 $SiO_2$  膜(誘電率 k=3.9)を上下に配した k=2.4 の多孔性 low-k 材料(p-SiOC)を層間絶縁膜とする Cu(バリア膜:Ta/TaN)配線パターン(配線ピッチ:100 nm)を用いた.図 1 には、試料の模式図を示す.配線パターンを含まない領域を併せて薄膜化し、プロセスダメージの無いリファレンス領域とした. $SiO_2$  膜を上下に挟んでいるのは、後述する、薄膜試料厚さの正確な計測を実施することを目的としている.断面試料作製は、集束イオンビーム(FIB)マイクロサンプリング法を採用した.加工の際には、正確なKKA 時の規格化のため、極力薄膜厚みを均一にするよう注意を払った.また FIB 加工による試料表面ダメージを減らすために、Ga イオンビームの加速電圧を5 kV に下げた仕上げ加工を行なった.

#### 2.1 STEM/EELS 測定

観察には、日本電子製 TEM/STEM 装置 JEM2100F 及び ARM200F を STEM モードで用いた. 通常の CEELS による 組成分析については、加速電圧 200 kV で実施したが、VEELS 測定では、冷陰極電界放出型電子銃(Cold-FEG)を 搭載した ARM200F を加速電圧 80 kV で使用した. VEELS 測定時の定型的なエネルギー分解能は 0.5 eVFWHM 程度である. 低加速電圧を採用する目的は、チェレンコフ放射の発生を抑制する点である.

#### 2.2 試料膜厚の測定

試料膜厚の測定には、ゼロロスピーク(ZLP)を含む低エネルギー損失領域のスペクトル、すなわち VEELS が必要である。薄膜試料の膜厚 t(nm) は、Log-Ratio 法 $^8$  により、次のように決定される:

$$t/\lambda = \ln(I_t/I_0) \tag{1}$$

ここで、 $I_0$  は全スペクトル強度及び ZLP の積算値であり、 VEELS 結果から取り出すことが出来る。 $\lambda$ (nm) は、非弾性 散乱の平均自由行程であり、材料の平均原子番号が判ってい

図1 Cu 配線/低誘電率 (low-k) 膜の溝状パターン模式図

れば、経験的に見積もることが可能である  $^{18}$ ). SiO $_2$  の場合では、加速電圧  $200 \, \mathrm{kV}$  の場合  $129 \, \mathrm{nm}$ 、加速電圧  $80 \, \mathrm{kV}$  で  $80 \, \mathrm{nm}$  である。同一の組成で同一の薄膜厚から得られた  $t/\lambda$  の実験値が違えば、材料の密度や空隙率が変化したと考えることが出来る。FIB 法により、均一な膜厚の試料で実測ができたとすれば、元来同一の $\lambda$  を持っている p-SiOC の相対厚さ  $t/\lambda$  の変化は、局所での密度や空隙率が変化したと見積もることが出来るはずである  $^{19}$ ).

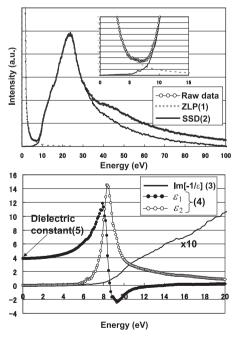

2.3 クラマースクローニッヒ解析による誘電率の測定概要 p-SiOC 膜 から 得 た VEELS から 誘 電 関 数 の 導 出 は、 Egerton が述べた KKA の手順に従って実施した  $^{8)}$ . 図  $^{2}$  に示すように、誘電率の導出は以下の  $^{5}$  つの手順に沿って実施される. (1) ZLP のフィッティング及び除去、(2) 多重散乱の除去、(3) 単一散乱強度(SSD)の規格化による損失関数の導出、(4) クラマースクローニッヒ変換による複素誘電関数の算出、(5) 誘電関数の実部  $\varepsilon_{1}$  の E=0 における数値を誘電率として抽出  $^{20}$ 、である.後述のように、チェレンコフ放射の影響が無視できるほど小さい場合は、ZLP の除去に特別な注意を払う必要は無い.筆者らは ZLP のフィッティングにはガウシアン+ローレンツィアンの混合カーブを用いている(図  $^{2}$ ).

ZLP の除去の後、フーリエログデコンボリューションにより多重散乱除去を行なって得た SSD は、以下の式で表すことが出来る。

$$SSD(E) = \frac{I_0 t}{\pi a_0 m_0 v^2} \quad Im \left[ \frac{-1}{\varepsilon(E)} \right] \quad In \left[ 1 + \left( \frac{\beta}{\theta_E} \right)^2 \right]$$

(2)

図 2 クラマース―クローニッヒ (KK) 解析手順. (1) ゼロロスピーク (ZLP) の除去, (2) 多重散乱の除去, (3) 単一散乱強度 (SSD) の規格化~エネルギー損失関数の導出, (4) KK 変換, (5) 複素誘電関数からの誘電率の抽出

#### 3. 結果と考察

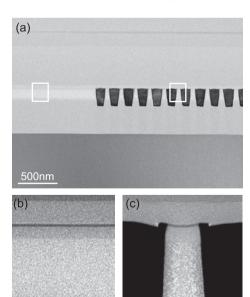

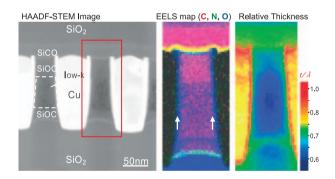

図3には、配線パターン断面の明視野 STEM 像を示す、パターン外(b)における SiOC 系 low-k 膜の領域において、多孔構造を示唆する低コントラストの粒状構造が観察されるが、配線パターン間(c)では、中央付近の孔径が大きくなっているのに加えて、側壁近傍 20 nm 程度での構造の緻密化が確認できる。図 4(b)には、CEELS を用いた配線間の C、N、O組成マップを示すが、側壁近傍 20 nm 程度の領域において、特にメチル基由来の C 脱離を確認することが出来る (矢印部).

#### 3.1 VEELS 測定結果

50nm

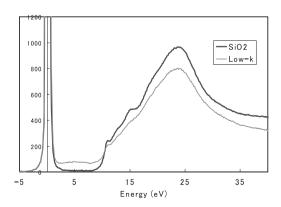

図 5 には、加速電圧  $80 \, \text{kV}$  で得た、 $SiO_2$  及び SiOC 系 low-k 膜の VEELS を示す。 $SiO_2$  において、バンドギャップ に相当する  $0 \sim 9 \, \text{eV}$  程度までの領域で、殆ど強度が存在しないことを確認することが出来る。 $Stöger-Pollach \, \text{ら}^{12)}$  によると、屈折率約  $2.0 \, \text{oO} \, SiO_2$  であれば、加速電圧  $80 \, \text{kV}$  でチェレンコフ放射は生じないので、より低屈折率である  $low-k \, \text{dV}$  料では生じないと断定することが可能である。すなわち、

図 3 p-SiOC (low-k) 膜配線パターンの明視野 STEM 写真 (a) 低倍率像, (b) パターン無し領域 (c) パターン領域

50nm

SiOC 膜における  $0 \sim 9$  eV 内の強度は、メチル基などの構造に起因するものであるといえる。

#### 3.2 クラマースクローニッヒ解析

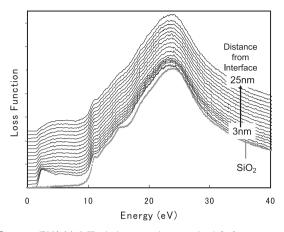

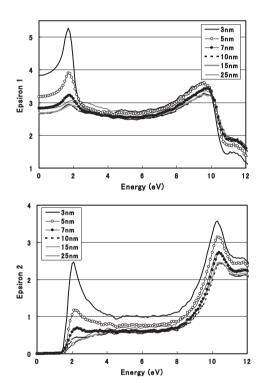

得られた VEELS(加速電圧 200 kV で取得)より、KKA 解析を実施した。図4 (c) には分析に用いた薄膜試料の相対 厚さマップを示す。これらの結果において、上下の $SiO_2$  層の $t/\lambda$  は 0.65 とほぼ一定であることを確認し、 $\lambda$ = 129 nm を 乗じて絶対膜厚 84 nm を得た。これにより(2)式における 規格化因子を決定して、エネルギー損失関数を導出し、クラマースクローニッヒ変換により複素誘電関数を得た。図 6 には、配線パターン端部における水平方向の位置分解 VEELS 結果から得た損失関数を、図 7 には複素誘電関数( $\varepsilon_1$  及び  $\varepsilon_2$ )の抜粋を示した。側壁から 10 nm 程度までの範囲で低エネルギー部のプロファイルに大きな変化が観測されており、配線プロセス時に C 抜けを伴う大きな構造変化を生じ、誘電率の上昇が生じたと考えられる。誘電関数の虚部( $\varepsilon_2$ )の観測により 2.5 eV 付近に強い吸収が生じていることから、欠陥準位の生成などが示唆される。

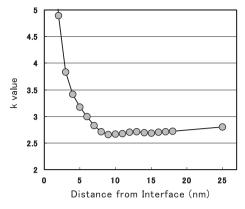

図8には、複素誘電関数の実部  $(\varepsilon_1)$  の E=0 における値 (誘電率)の変化を配線側壁から 25 nm 位置まで示した.これらの結果から、誘電率は水平方向、配線側壁付近での上昇が顕著であることがわかる.プロセス検討の結果、バリアメタル被覆プロセスでのダメージが問題となることが判明した.

図4 Cu 配線/p-SiOC(low-k)膜パターン部の STEM-EELS 分析結果. (a) HAADF-STEM 像, (b) C, N, O の EELS イメージング結果(矢印部分で C 強度低下), (c) VEELS より得た相対厚さ  $(t/\lambda)$  マップ

図5 加速電圧 80 kV, Cold-FEG 搭載の STEM 装置より得たSiO<sub>2</sub> 及び p-SiOC 系低誘電率(low-k)材料の VEELS

図 6 Cu 配線側壁界面(Interface)から水平方向  $3\sim25\,\mathrm{nm}$  における位置分解 VEELS 結果(エネルギー損失関数で表示)

図7 Cu 配線側壁界面(Interface)から水平方向  $3\sim 25~\rm nm$  における位置分解 VEELS より導出された複素誘電関数. (a) 実部  $(\epsilon_1)$ , (b) 虚部  $(\epsilon_2)$

#### 4. まとめ

VEELS を用いたクラマース一クローニッヒ解析により、配線パターンを施した低誘電率相関絶縁膜の局所誘電率測定を実施した. 加速電圧 80 kV における測定により、チェレンコフ放射による低エネルギー損失領域のスペクトル変調を抑制し、薄膜厚さ制御によるエネルギー損失関数の正確な導出の結果、配線側壁付近約 10 nm 領域での、加工プロセスによると思われる誘電率上昇を検出することが出来た. 本解析では、誘電率上昇に繋がる直接的な構造変化についての解析が実施できていないが、プロセス最適化のための実用的手段として、VEELS 領域はもっと普及できると考える. 特に、

図8 Cu 配線側壁界面から水平方向  $2\sim25\,\mathrm{nm}$  における局所誘電率の変化

80 kV という通常の材料解析では低い加速電圧を採用すること、加えて電子源に Cold-FEG を採用することで、ゼロロスピークのフィッティングや除去も非常に容易となる。今後、ELNES 解析などを組み合わせることで、ダメージ構造の解明を進めて行く予定であるが、非晶性材料やソフトマテリアルの評価においては、引き続きダメージ抑制や構造モデル構築には多くの解決すべき課題が存在する。なお、本測定で得た誘電率は、高速電子線が励起する電子分極成分のみに関連するものであり、イオン分極や配向分極成分などを含めたものとは本質的に異なっていることにも留意する必要がある。

#### 文 献

- Haruta, M., Kurata, H., Komatsu, H., Shimakawa, Y. and Isoda, S.: Phys. Rev. B, 80, 165123-1-6 (2009)

- Tanaka, I. and Mizoguchi, T.: J. Phys.: Condens. Matter., 21, 104201– 104209 (2009)

- 3) Ikeno, H., Mizoguchi, T., Koyama, Y., Kumagai, Y. and Tanaka, I.: *Ultramicroscopy*, 106, 963–1168 (2006)

- 4) Kawasaki, N., Sugiyama, N., Otsuka, Y., Hashimoto, H., Tsujimoto, M., Kurata, H. and Isoda, S.: *Ultramicroscopy*, **108**, 399–406 (2008)

- Kimoto, K., Nagai, T., Saito, M., Matsu, Y. and Ishizuka, K.: *Nature*, 450, 702–704 (2007)

- Batson, P.E., Dellby, N. and Krivanek, O.L.: Nature, 418, 617–620 (2002)

- Nellist, P.D., Chisholm, M.F., Lupini, A.R., Borisevich, A., Sides, Jr. W.H., Pennycook, S.J., Dellby, N., Keyse, R., Krivanek, O.L., Murfitt, M.F. and Szilagyi, Z.S.: *J. Phys.*, 26(1), 7–12 (2006)

- 8) Egerton, R.F.: in Electron energy loss spectroscopy in the electron microscope, 2nd edn. Plenum, New York: 277–288 (1996)

- Park, J., Chung, S.H.J.-G., Kim, H., Lee, H., Kim, K. and Park, G.-S.: *Ultramicroscopy*, 109, 1183–1188 (2009)

- 10) Potapov, P.L., Engelmann, H.-J., Zschech, E. and Stoger-Pöllach, M.: *Micron*, 40, 262–268 (2009)

- 11) Egerton, R.F.: Ultramicroscopy, 107, 575–586 (2007)

- Stöger-Pollach, M., Franco, H., Schattschneider, P., Lazar, S., Schaffer, B., Grogger, W. and Zandbergen, H.W.: *Micron*, 37, 396–402 (2006)

- 13) Stöger-Pollach, M.:  $\mathit{Micron}$ , 39, 1092–1110 (2008)

- 14) Maex, K., Baklanov, M.R., Shamiryan, D., Iacoppi, F., Brongersma, S.H. and Yanovitskaya, Z.S.: J. Appl. Phys., 93, No. 11, 8793–8841 (2003)

- 15) Richard, O., Iacoppi, F., Bender, H. and Beyer, G.: *Microelectronic Engineering*, 84, 517–523 (2007)

- 16) Aimadeddine, M., Arnal, V., Farcy, A., Guedj, C., Chevolleau, T., Posseme, N., David, T., Assous, M., Louveau, O., Volpi, F. and Torres, J.: *Microelectronic Engineering*, 82, 341–347 (2005)

- 17) Otsuka, Y., Shimizu, Y. and Tanaka, I.: J. Electron Microsc., 58:

- 29-35 (2009)

- 18) Malis, T., Cheng, S.C. and Egerton, R.F.: J. Electron Microsc. Tech., 8, 193–200 (1988)

- Otsuka, Y., Shimizu, Y., Kawasaki, N., Ogawa, S. and Tanaka, I.: *Jpn. J. Appl. Phys.*, 49, 111501–111504 (2010)

- 20) Lo, S.-C., Kai, J.-J., Chen, F.R., Chang, L., Chen, L.-C., Chiang, C.-C., Ding, P., Chin, B., Zhang, H. and Chen, F.: *J. Electron Microsc.*, 50, 497–507 (2001)

122 顕微鏡 Vol. 47, No. 2 (2012)